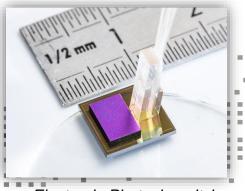

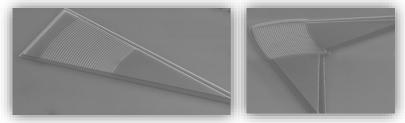

Photonic Integrated Circuit (PIC)

Submicron Silicon core waveguide

# LETI MPW OFFER AND CONCLUSION

**Leti Innovation Days 2018 workshop**

Christophe KOPP | 02/07/2018

# SILICON PHOTONICS: TECHNOLOGY OVERVIEW

Silicon **Implantation**

activation

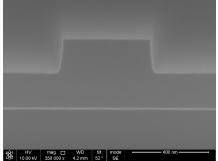

Silicon **Patterning**  Define all the photonic devices

Modulator junction formation &

Germanium **Epitaxy**

Germanium

**Implantation**

Several silicon thicknesses and waveguide

Photodetector patterning

Germanium selective epitaxy

silicidation

architectures

Photodetector contact formation

CMOS-based process with photonic

dedicated optimizations

process

Si Modulator contact CMOS standard

Silicidation

Metal interconnection

Metal heater definition for wave length tuning

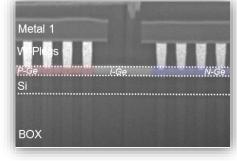

Si Substrate

**BEOL**

Silicon BOX Silicon Substrate

> Silicon On Insulator (SOI) substrate: Ø8" or Ø 12"

Cleanroom facilities (Leti)

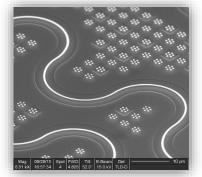

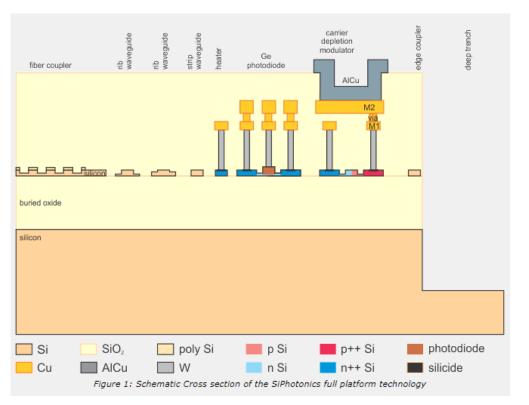

W-Via Grating Coupler Wave Guides PN Junction Modulator Ge PhotoDiode Shallow Rib Strip Deep Rib

Silicon Photonic Process Flow

Schematic cross section of a silicon photonic circuit (Leti)

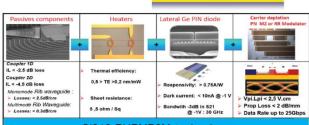

# **SILICON PHOTONICS: TYPICAL DEVICES**

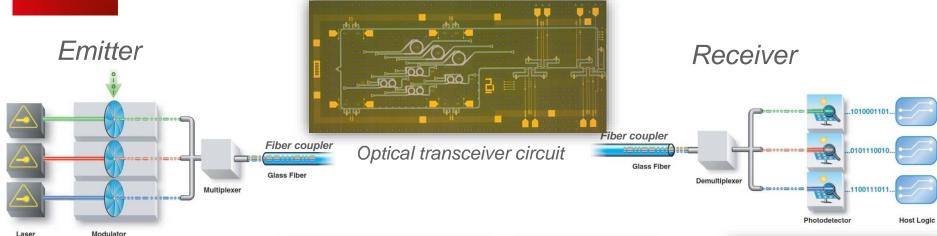

High speed modulator

Fibre coupler

High speed photodetector

Wavelength multiplexer

Tunable filter

# **SILICON PHOTONICS: FOUNDRIES**

## **R&D** foundries

- AIM Photonics (US)

- IHP (Germany)

- IME (Singapore)

- 220nm SOI platform

- IMEC (Belgium)

- 220nm SOI platform

- LETI (France)

- 300nm SOI platform

- PETRA (Japan)

- VTT (Finland)

- 3μm and 12 μm SOI platform

## **Industrial foundries**

INTEL (US)

Luxtera (Freescale, US)

Samsung (Korea)

ST-Microelectronics (France)

# **R&D MPW offers**

CMP (France)

Europractice/Epixfab (EU)

MOSIS (US)

A. E. J. Lim et al., "Review of Silicon Photonics Foundry Efforts," IEEE Journal of Selected Topics in Quantum Electronics, vol. 20, no. 4, pp. 405–416, Jul. 2014.

# **IMEC MPW OFFER**

#### imec-ePIXfab SiPhotonics: iSiPP50G

| Module         | Specification                                        |

|----------------|------------------------------------------------------|

| Substrate      | 220nm SOI                                            |

| SOI patterning | 3 etch depth levels<br>Minimum line and space: 150nm |

| Poly-Si        | Deposition and patterning                            |

| Doping         | 4-level N and P                                      |

| Germanium      | Photodiodes, electro-absorption modulators           |

| Contacts       | W contact plugs on silicide                          |

| M1, VIA and M2 | Standard CMOS metallization                          |

| Bondpads       | Standard AlCu bondpads                               |

| BEOL openings  | Edge couplers                                        |

# □ SOI 220nm/2µm (BOX)

- Substrate: SOI with 220nm Si, 2um buried oxide

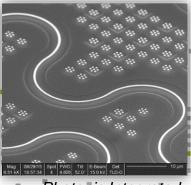

- WG module (WaveGuide): 220nm full Si etch for strip waveguides, photonic crystals, etc.

- FC module (FiberCoupler): 70nm partial Si etch for fiber couplers, rib waveguides, etc.

- SK module (Socket): 150nm partial Si etch

- Poly-Si module: extra etch-level for efficient fiber couplers

- 4 P and N-type doping levels for **electro-optic modulator** design and heaters for thermo-optic modulation

- Ge photodiodes as detectors

- High speed Ge electro-absorption modulators

- 2 levels of metal interconnect

- · Edge coupler

# **AIM MPW OFFER**

# Silicon Photonics Multi Project Wafer (MPW

- MPW Fab Runs Planned in 2017

- SUNY Poly 300mm fab line

- 3 MPW offerings

- Full-Active- 2 planned in 2017

- Passive Only- 2 planned in 2017

- Interposer- 1 planned in 2017

- Reservations to be a rider can be started at

http://www.aimphotonics.com/pdk-mpw-sign-up/

- Generates quote with terms

- 20% down to hold slot; balance invoiced at design submission

- MOSIS is the MPW Aggregator

- DRC clean designs are submitted to MOSIS

- MOSIS also distributes the PDK

- MPW Pricing

#### **FULL**

- 50mm<sup>2</sup> chips

- \$100K AIM members

- \$120K non-members

- 8mm<sup>2</sup> chips

- \$25K AIM members

- \$30K non-members

#### PASSIVE

- 50mm2 chips

- \$30K AIM members

- \$36K non-members

#### INTERPOSER

- 156mm2

- \$93.6K AIM members

- \$112.3K non-members

**□** SOI 220nm/2μm (BOX)

# **IME MPW OFFER**

# Institute of Microelectronics

#### SILICON PHOTONICS MULTIPLE-PROJECTS WAFER

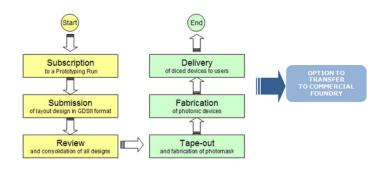

#### Types of Service:

Shared Prototyping Runs: Participants will share the cost of the prototyping efforts and have the option of using either IME's or their own design, on the proviso that it is within technical specifications.

Schedule: January, May and September each year.

To participate in the next shared prototyping run, please contact us for details.

. Customised Prototyping Runs: This service is intended for user whose requirements are beyond the timeline and technical specifications of the Shared Prototyping Runs. For Customised Prototyping, please contact us for more information and to arrange a discussion.

#### Flow:

#### MULTIPLE-PROJECTS WAFER (MPW) SERVICES

IME Multiple-Projects Wafer (MPW) is a one-stop solution for low cost prototying and low volume production. Designs from multiple customers are combinedinto one mask set and wafer lot. This allows costs to be shared across a number of program participants and provides a cost-effective method for prototype and proof-of-concept silicon.

Contact person:

Dr. Patrick Lo Guo Qiang Institute of Microelectronics, Singapore logq@ime.a-star.edu.sg

Phone: +65-67705705

■ SOI 220nm/2µm (BOX)

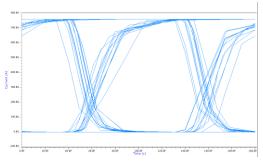

# **LETI MPW OFFER**

1

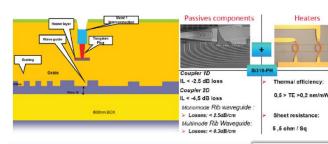

# Si310-PH: Passif and heaters: friendly packageable

www.europractice-ic.com / SiPhotonics\_technology\_LETI\_passives\_w\_heater.php

#### Key features

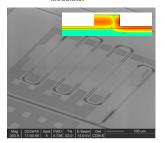

- Passive structures (3 mask layers DUV 193nm)

- CD min 120nm

- 300nm /150nm -> see cross section 1

- 150nm /0 -> see cross section 1

- Optional Slab 65nm (Deep Rib)

- Ti/ TiN Heater layer

- W vias

- 1 Metallization for routing

- · Final passivation with pad opening

Si310-PH technology

□ SOI 300nm/800nm (BOX)

2

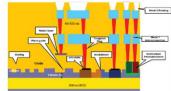

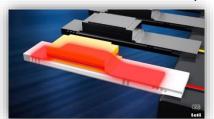

#### Si310-PHMP2M: Full platform: friendly packageable

comp

http://cmp.imag.fr/

- High performance building blocks

- Compatible with 3D integration

- PDKs available via Cadence,

Phoenix software, Mentor

Graphics, and Pyxis

- □ Technology compatible design rules with 300 mm industrial foundry

#### **Key features**

- Passive structures (3 mask layers DUV 193nm)

- CD min 120nm

- 300nm /150nm -> see cross section 1

- 150nm /0 -> see cross section 1

- Optional Slab 65nm (Deep Rib)

- Ti/ TiN Heater layer

- · Germanium PD's fabrication

- n and p implant level

- MZ and RR Modulators

- 4 level implants

- Silicidation

- W vias

- · 2 Metallization BEOL for routing

- Final passivation with pad opening

- Friendly Packageable

- Compatible for UBM fabrication for electronic integration

Si310-PHPMP2M technology

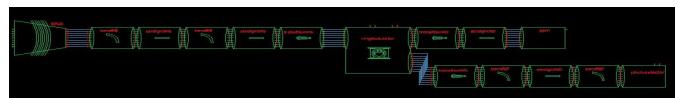

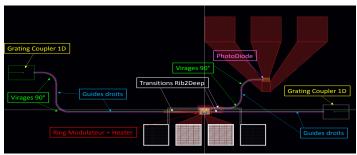

# CIRCUIT DESIGN KIT AT LETI

# cādence GMenter

### Library of available components

- Cadence/Virtuoso and Mentor/Calibre + Eldo framework

- Phoenix software

- Pyxis/LUMERICAL

**PDK Photonics** Models, Schematic circuit simulation, Layout, Verification, Layout finishing

Schematic view

Layout view

Circuit simulation

<sup>&</sup>quot;Multiple wavelength silicon photonic 200mm R&D platform for 25Gb/s and above applications", Szelag et al., Photonics Europe 2016

"Verilog-A passive and active components modeling for silicon photonic circuits process design kit (PDK) assembly", Karakus et al., Photonics West 2016

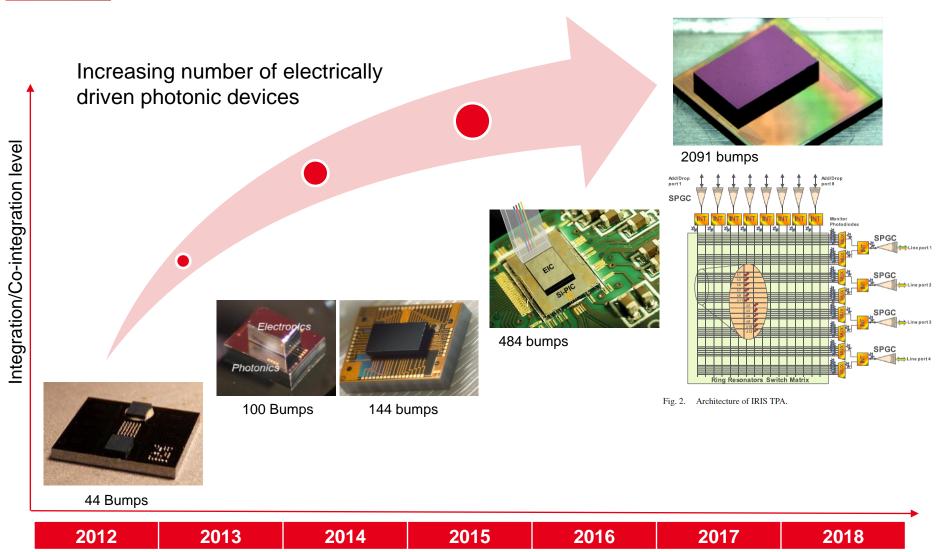

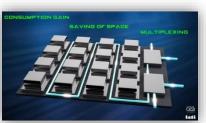

# **TOWARDS HIGHER INTEGRATION LEVEL**

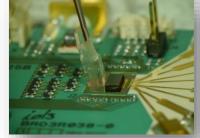

# TOWARDS ON CHIP INTEGRATION

Discrete component assembly

Micro-bench

Integration and 3D assembly with electronics

Switch & Network on chip

1990

2000

2010

2020

Axsun

Hymite

Intexys / CEA

CEA

Network on chip

Heterogeneous integration

Multilayer photonics

# Leti Innovation Days July 4-5, 2018

Thank you for your attention

Commissariat à l'énergie atomique et aux énergies alternatives Minatec Campus | 17 rue des Martyrs | 38054 Grenoble Cedex | France www.leti.fr