#### **3D INTEGRATION, A SMART WAY TO ENHANCE PERFORMANCE**

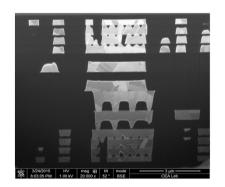

<u>3D VLSI technologies</u> (3D VIA Pitch <5µm)

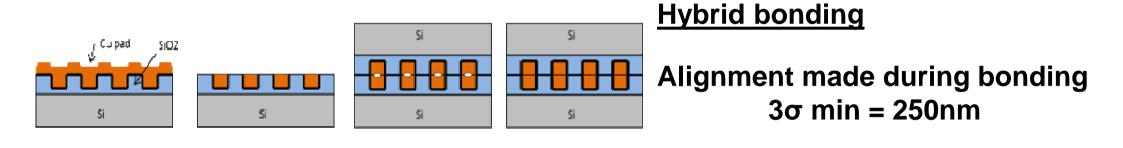

#### Hybrid bonding

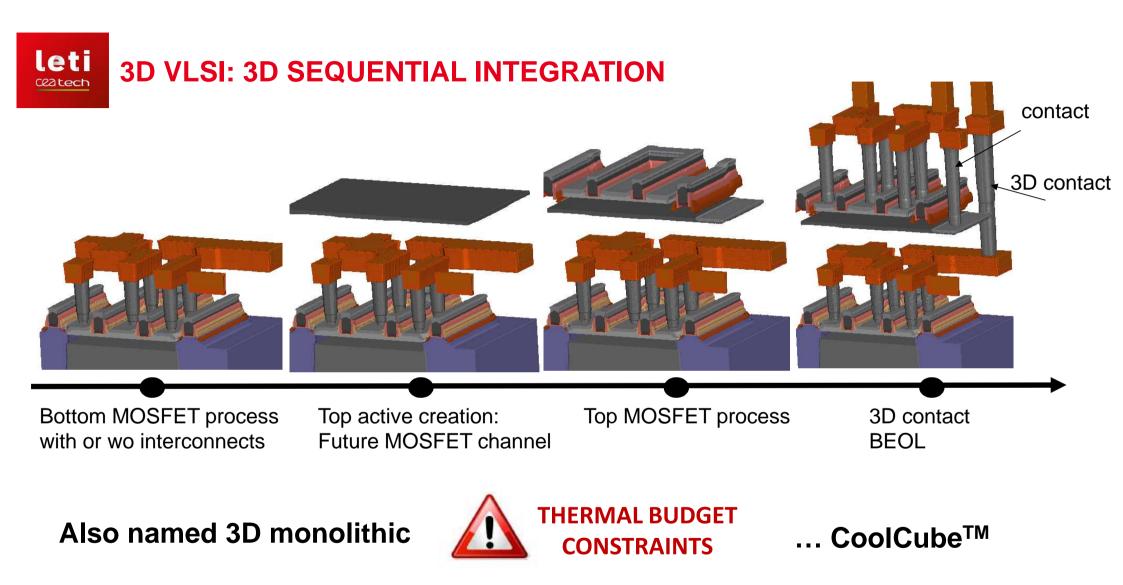

#### **3D** sequential

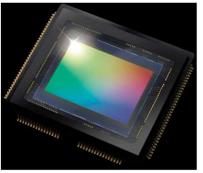

Image sensor

HPC

How these technologies can boost

- 3D VLSI technologies: from hybrid bonding to 3D sequential integration

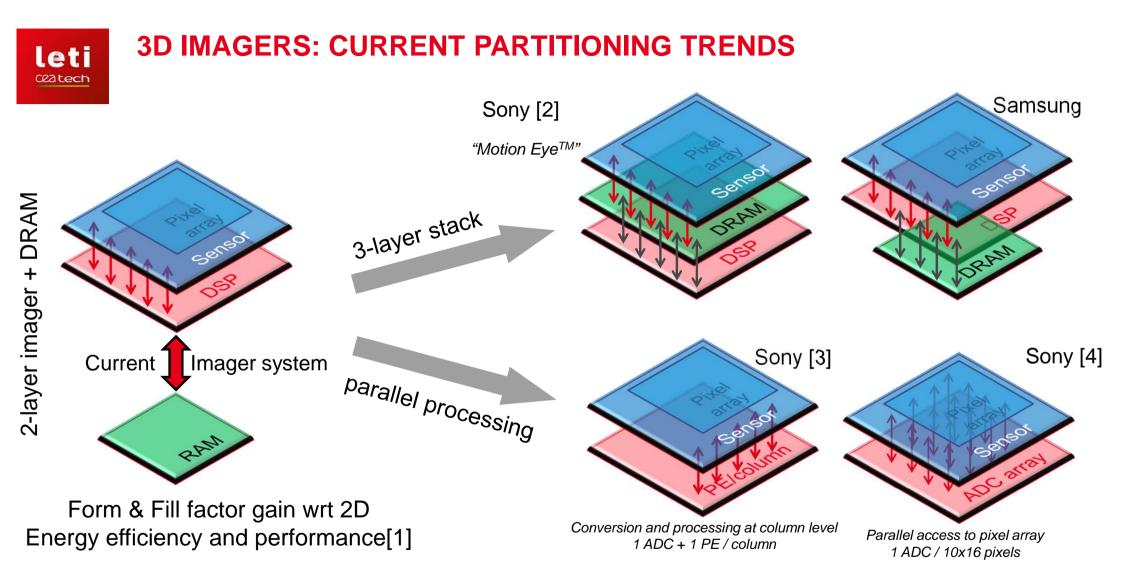

- 2 3D imagers

- 3 High Performance computing

# **3D VLSI: HYBRID BONDING AND 3D SEQUENTIAL OPTIONS**

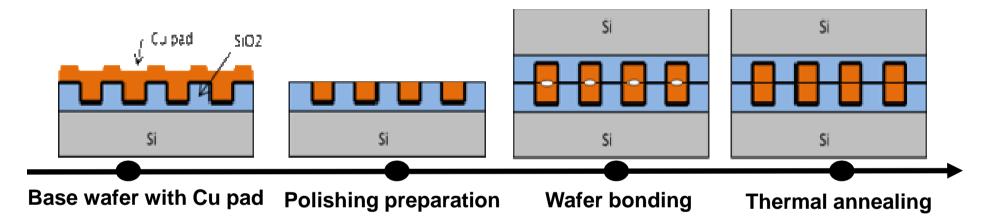

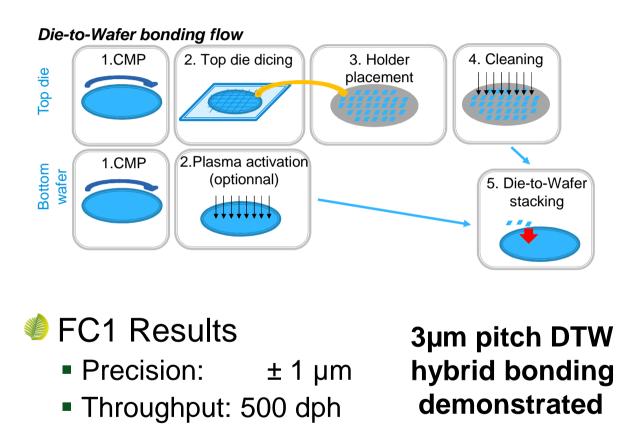

#### Hybrid bonding flow:

leti

Ceatech

Various options: Wafer to Wafer, Die to Wafer, Die to Die

leti

#### **3D VLSI: HYBRID BONDING VERSUS 3D SEQUENTIAL**

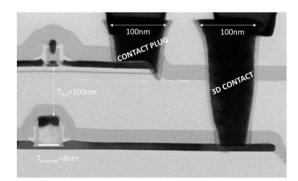

**3D sequential**

Alignment by lithography  $3\sigma = 5$ nm (28nm stepper)

leti <sup>Ceatech</sup>

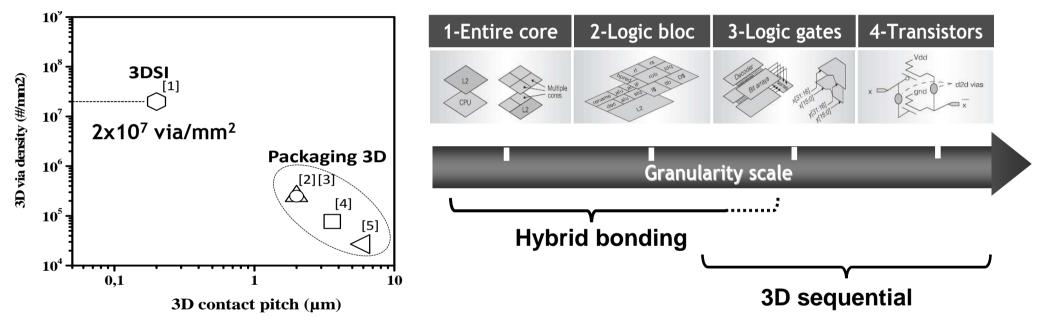

## **3D VLSI: HYBRID BONDING & 3D SEQUENTIAL OPTIONS: VIA DENSITY**

#### 3D via density

3D partitioning options

[1]: L. Brunet et al., VLSI 2016, [2] I. Sugaya et al., ASMC 2015, [3] J. De Vos, 3DIC 2016 [4] L. Peng et al., EPTC 2016 [5] D. Zhang et al. TSM 2015

- 3D VLSI technologies: from hybrid bonding to 3D sequential integration

- 2 3D imagers

- 3 High Performance computing

[1] Retine leti [2] SONY ISSCC 2017 [3] SONY ISSCC 2017, [3] SONY VLSI 2017

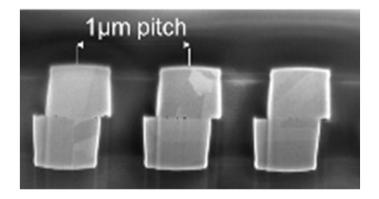

**HYBRID CU BONDING (WTW)**

#### Alignment

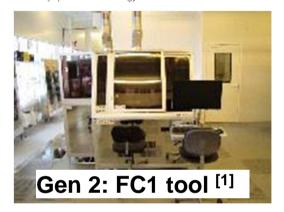

**Co-development equipment/process**

Advanced bonding tool generation (Gemini)

$\rightarrow$  Alignement performance:  $3\sigma = 195$ nm

1µm pitch Hybrid Bonding

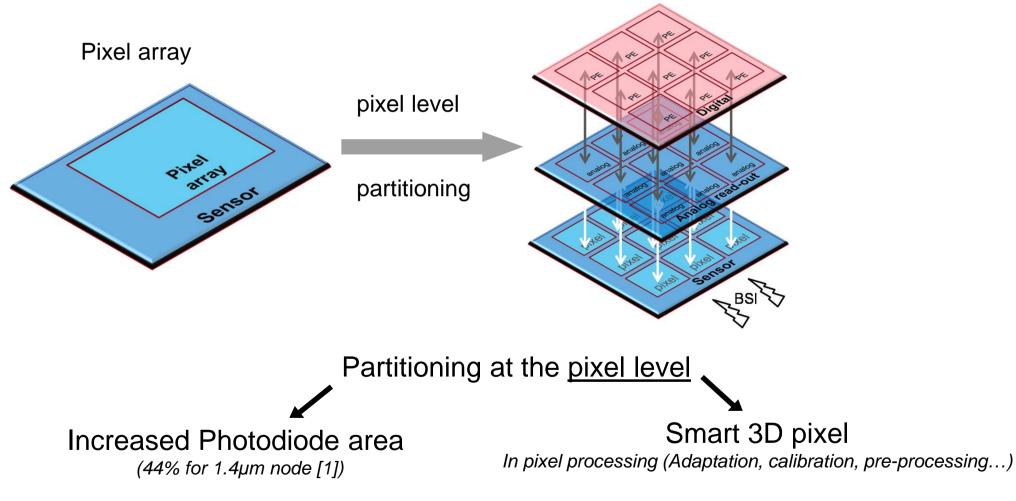

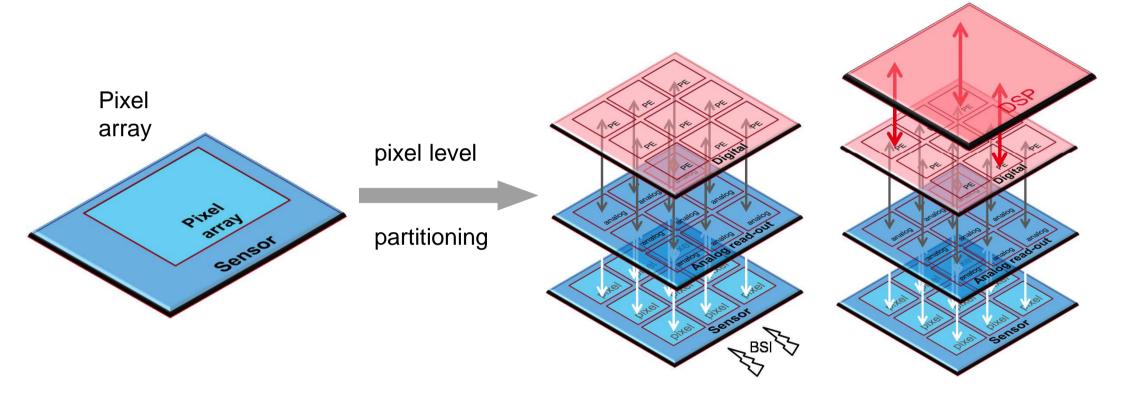

#### **3D IMAGERS: NEW PARTITIONNING OPPORTUNITIES**

#### **3D IMAGERS: NEW PARTITIONNING OPPORTUNITIES**

Hybrid bonding can be used to connect the 3D pixel to the DSP and RAM

<1 $\mu$ m 3D contact pitch  $\longrightarrow$  3D sequential integration

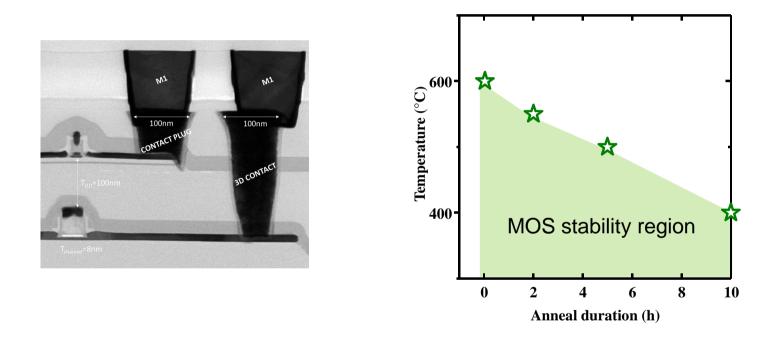

300 mm industrial clean room demonstration Max TB budget is relaxed for a photodiode (700°C) <sup>[1]</sup> vs MOSFET (500°C)

[1]P. Coudrain et al., IEDM 2008

leti

#### **3D IMAGERS: NEW PARTITIONNING OPPORTUNITIES**

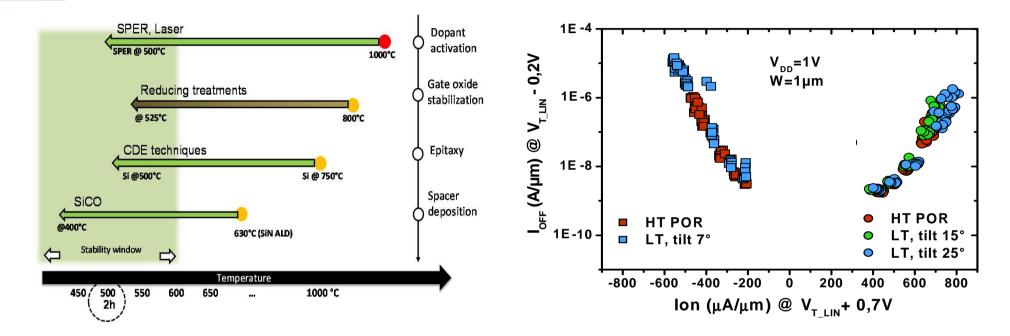

#### Critical process modules are now below 500℃

Cold 28nm FDSOI devices in line with high-temp. POR

- 3D VLSI technologies: from hybrid bonding to 3D sequential integration

- 2 3D imagers

- **3** High Performance Computing

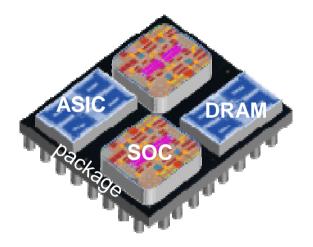

**REVISITING HPC CHIPS ARCHITECTURE**

**Complex SOC for HPC application**

let

Ceatech

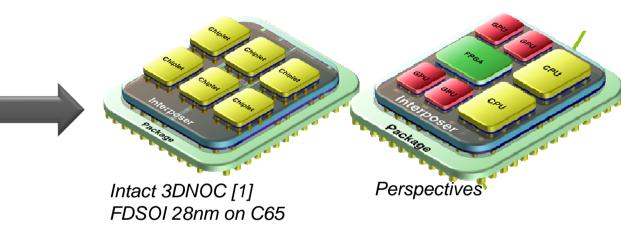

Huge die size (4cm<sup>2</sup>) (yield issues) Complexity wall (co-integration of technologies) Memory wall Leti's roadmap: Chiplets on active interposer

Cost reduction:

Smaller chips (improved Yield) Known good die (pre bond test) Each technology at the right silicon cost

Performance: Best technology for each chip Compatible with HBM

[1]: P. Vivet et al., ISSCC 2016 (leti)

leti <sup>Ceatech</sup>

#### **DIE TO WAFER WITH SCALED CONTACT PITCH**

[1] P. Metzger & Al « Toward a flip-chip bonder dedicated to direct bonding for productionenvironment », IWLPC 2017.

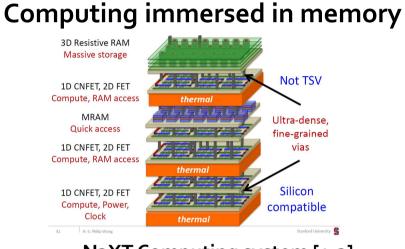

# THE ULTIME IMBRICATION OF MEMORY AND COMPUTING

#### ightarrow 3D sequential is an opportunity to break the memory wall

leti

Ceatech

N3XT Computing system [1,2]

#### X 1000 gain in consumption expected with computing near memory

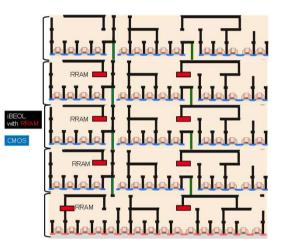

#### Neuromorphic computing

# Brain-inspired computing cube

High contact density mimics the high interconnectivity of neurons

RRAM mimics the synapses

[1] Shulaker et al., IEDM 2014, [2] Aly et al., Rebooting computing, 2015

## **CONCLUSION: LETI 3D OFFER**

• Every application recquiring a high number of interconnections or reconfigurability of the interconnections deserves to be explored in 3D

Neuromorphic

Accelerators

Displays

Implants & Wearables

HPC.

Imagers

Lighting

- Leti is your partner to evaluate the gains for your applications using 3DVLSI

- Demonstration of prototypes & Architecture partitionning

# Thank you for your attention